CAIE AS and A Level CS revision - Unit 4 (2nd)

如遇到公式加载异常,请刷新页面!

Unit 4 Processor Fundamentals 处理器基础

4.1 Central Processing Unit (CPU) Architecture 中央处理器(CPU)架构

- 大纲要求

4.1.1 Show understanding of the basic Von Neumann model for a computer system and the stored program concept 了解计算机系统的基本冯诺依曼模型和存储程序概念

- Von Neumann model:冯诺依曼模型,指描述计算机系统结构的模型,由数学家冯·诺依曼提出。

- 模型基本特征如下:

- There is a processor - the central processing unit (CPU). 一个处理器,即中央处理单元(CPU)。

- The processor has direct access to memory. 处理器直接访问内存。

- The memory contains a ‘stored program’ (which can be replaced by another at any time) and the data required by the program. 内存包含一个“存储程序”和程序所需的数据。

- The stored program consists of individual instructions. 存储的程序由单独的指令组成。

- The processor executes instructions sequentially. 处理器按顺序执行指令。

- 模型基本特征如下:

4.1.2 Show understanding of the purpose and role of registers, including the difference between general purpose and special purpose registers 了解寄存器的用途和作用,包括通用寄存器和专用寄存器的区别

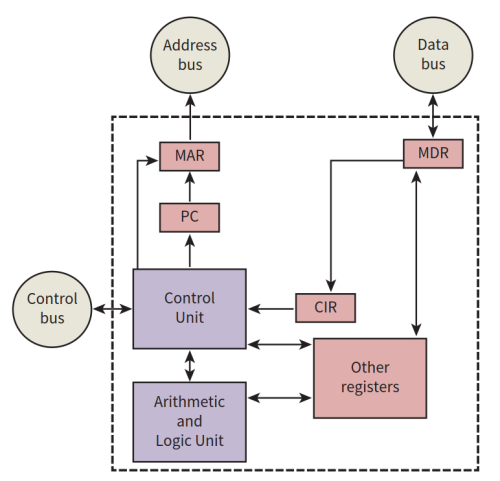

- Special purpose registers including: 特殊用途寄存器包括:

- Program Counter (PC) 程序计数器 (PC)

- Memory Data Register (MDR) 内存数据寄存器 (MDR)

- Memory Address Register (MAR) 内存地址寄存器 (MAR)

- The Accumulator (ACC) 累加器 (ACC)

- Index Register (IX) 索引寄存器 (IX)

- Current Instruction Register (CIR) 当前指令寄存器 (CIR)

- Status Register 状态寄存器

- Program Counter (PC) 程序计数器 (PC)

- Register:寄存器,指CPU内部用来存放数据的一些小型存储区域,用来暂时存放参与运算的数据和运算结果。

- General purpose register:通用寄存器,指没有指定用途的寄存器,在使用时可用来存储任何用途的数据。常见的通用寄存器包括:

- The Accumulator (ACC):累加器,指存储运算前和运算后数据的存储单元。

- Special purpose register:专用寄存器,指有指定用途的寄存器,存储指定的数据。常见的专用寄存器包括:

- Program Counter (PC):程序计数器,指储存着从存储器中取出的下一个指令地址的寄存器。

- Memory Data Register (MDR):内存数据寄存器,用于寄存将要写入到计算机主存储器或由计算机主存储器读取后的数据。

- Memory Address Register (MAR):内存地址寄存器,用于保存当前CPU所访问的内存单元的地址。

- Index Register (IX):变址寄存器,指用于存放存储单元在段内偏移量的存储单元。用它们可实现多种存储器操作数的寻址方式,为以不同的地址形式访问存储单元提供方便。

- Current Instruction Register (CIR):现行指令寄存器,指存储当前指令以便后续进行运算和分析的存储单元。

- Status Register(SR):状态寄存器,用于保存由算术指令和逻辑指令运行或测试结果建立的各种状态码。

- General purpose register:通用寄存器,指没有指定用途的寄存器,在使用时可用来存储任何用途的数据。常见的通用寄存器包括:

4.1.3 Show understanding of the purpose and roles of the Arithmetic and Logic Unit (ALU), Control Unit (CU) and system clock, Immediate Access Store (IAS) 了解算术和逻辑单元 (ALU)、控制单元 (CU) 和系统时钟、立即存取存储 (IAS) 的用途和角色

- Arithmetic and Logic Unit (ALU):算术和逻辑单元,指负责运行程序中指令的算术或逻辑处理要求的单元。ALU从寄存器中调取和存储数据,将结果反馈给控制单元,以便其控制和执行各项指令。

- Control Unit (CU):控制单元,指控制处理器和其他部分的数据流,并正确处理指令的单元。控制单元用clock时钟来控制进程的同步。时钟的分类如下:

- Internal clock:内部时钟,指控制处理器内部活动周期的时钟。

- system clock:系统时钟,指控制处理器外部活动周期的时钟。

- Immediate Access Store (IAS):立即存取存储,用于储存用户现在正在使用的数据与程序。由于处理器的运行速度远快于计算机的其他部分,因此需要提前将需要的数据先存放在该单元内,以便加快计算速度。

4.1.4 Show understanding of how data are transferred between various components of the computer system using the address bus, data bus and control bus 了解如何使用地址总线、数据总线和控制总线在计算机系统的各个组件之间传输数据

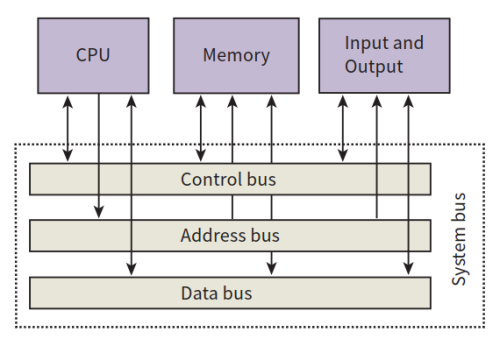

- System bus:系统总线,用于连接CPU与内存和输入/输出装置。系统总线由以下三类构成:

- address bus:地址总线,指用于传输地址的组件。其将MAR传输出的地址传递给内存或输入/输出设备,以便定位相关数据。

- 注意:地址总线是one-way street单向的,只能从MAR传到内存或输入/输出设备,不能反向操作。

- data bus:数据总线,指用于传输数据的组件。其能够将MDR传输出的数据传递给内存,也能将内存的值传回CPU。

- 注意:数据总线是two-way(bidirectional)双向的。

- control bus:控制总线,指用于传输控制信号的组件。其能够将control unit控制单元发出的信号传递给其他系统组件,也能将其他系统组件的信号传回控制单元。

- 注意:控制总线是two-way(bidirectional)双向的。

- 控制总线一般以计算机的time cycle为周期来传输timing signal定时信号,以保证发送信息端与接收信息端能够同步。

- address bus:地址总线,指用于传输地址的组件。其将MAR传输出的地址传递给内存或输入/输出设备,以便定位相关数据。

- 三类总线对CPU、memory内存和input/output输入/输出设备的串连示意图:

- CPU内部各组件及其关系的图像如下图所示:

4.1.5 Show understanding of how factors contribute to the performance of the computer system 了解因素如何影响计算机系统的性能

Including: 包括:

· processor type and number of cores 处理器类型和内核数量

· the bus width 总线宽度

· clock speed 时钟速度

· cache memory 高速缓存

- 影响计算机系统性能的因素包括:

- processor type and number of cores 处理器类型和内核数量:多核处理器的每一个内核都是一个独立的处理器,因此内核数量越多,性能越高。

- the bus width 总线宽度:地址总线中,总线宽度越高,能用于寻址的位置越多,性能越高;数据总线中,理想的总线宽度应与word length字长位数保持一致。如果无法保持一致,则应为字长位数的一半,以便保证将内容分两次完整传输,但性能下降。

- word length:字长,表示CPU一次能并行处理的二进制位数。通常是16 bits,32 bits或64 bits。

- clock speed 时钟速度:时钟速度决定了任何操作可以采取的最短时间,时钟速度越快,说明反应时间越短,性能越高。但由于其他组件的处理速度无法像处理器一样快,因此需要IAS立即存取存储的参与。

- cache memory 高速缓存:缓存区提前调用或储存数据以备后续快速提取使用,因此高速缓存越大、访问速度越快,性能越高。

4.1.6 Understand how different ports provide connection to peripheral devices 了解不同端口如何提供与外围设备的连接

Including connection to: 包括连接:

· Universal Serial Bus (USB) 通用串行总线 (USB)

· High Definition Multimedia Interface (HDMI) 高清多媒体接口 (HDMI)

· Video Graphics Array (VGA) 视频图形阵列 (VGA)

- 各输入/输出设备与CPU的连接需要经过device controller设备控制器,设备控制器上有ports端口,分别连接CPU与输入/输出设备。

- 如果输入/输出设备在计算机内部,则该端口称为internal ports内部端口;如果输入/输出设备在计算机外部,则该端口称为external ports外部端口。外部的设备通过外部端口与计算机相连,进行数据传输。

- 常见的外部端口包括:

- Universal Serial Bus (USB) 通用串行总线:

- 能够实现plug-and-play即插即用技术,在计算机开启状态下插入即可自动识别并使用,消除了设备的专业识别技术限制。

- 支持连接层级结构,计算机位于该结构的root根部,能够同时支持127个不同的外接设备。

- USB技术在不断发展。

- High Definition Multimedia Interface (HDMI) 高清多媒体接口:当需要使用第二屏幕投影时,能够通过该端口进行高分辨率的屏幕显示。

- 注意:该端口能够同时进行音频和视频的传输。

- Video Graphics Array (VGA) 视频图形阵列:当需要使用第二屏幕投影时,能够通过该端口进行高分辨率的屏幕显示。

- 注意:该端口不直接提供音频传输,如果播放视频,需要额外连接音频输出。

- Universal Serial Bus (USB) 通用串行总线:

4.1.7 Describe the stages of the Fetch-Execute (F-E) cycle 描述 Fetch-Execute (F-E) 循环的阶段

Describe and use ‘register transfer’ notation to describe the F–E cycle 描述和使用“寄存器转移”符号来描述 F-E 循环

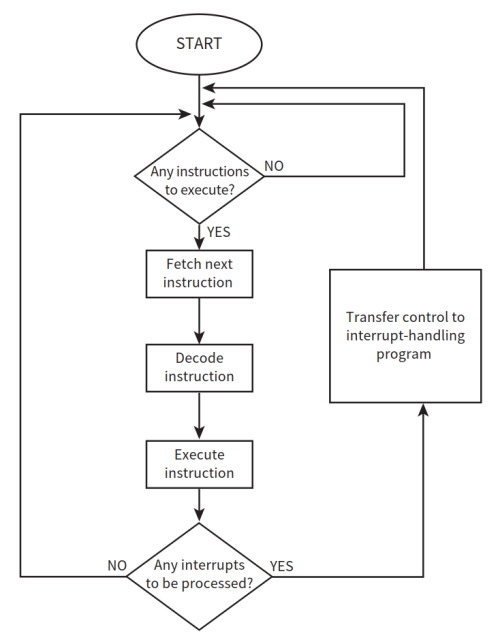

- Fetch-Execute (F-E) cycle:取译码执行循环,是冯诺依曼模型下的计算机处理器运行结构。

- Fetch stage取码阶段:每个时钟周期内将进行一次从存储器调用数据的过程。

- 如果程序正常运行,则即将取用的指令地址已经被存放于program counter(PC)程序计数器内。

- PC中存放的数值被传送到CPU中的MAR内。

- Fetch stage取码阶段:每个时钟周期内将进行一次从存储器调用数据的过程。

- MAR ← [PC] (PC中的数值被送入MAR)

- MAR对应地址中的数据被传送到MDR内;同时,PC取用下一条指令的地址。

- PC ← [PC] + 1; MDR ← MAR (PC调用下一条数值,MAR将地址查找出的数值传给MDR。二者同时发生。)

- MDR中的数据被传送到CIR内,准备进行解码和执行。

- CIR ← [MDR] (MDR中的数值被送入CIR)

- Decode stage解码阶段:

- CIR中的指令被传送到control unit控制单元,由控制单元根据指令内容,发送该指令到相应的组件,以便进行接下来的执行阶段。如果解码过程中需要进行算术或逻辑处理,则ALU算术与逻辑单元将会参与进来。

- Execute stage执行阶段:

- 使用汇编语言等进行指令的执行。【参考4.2】

- Decode stage解码阶段:

- Fetch-Execute (F-E) cycle的运行过程如下图所示:

4.1.8 Show understanding of the purpose of interrupts 展示对中断目的的理解

Including: 包括:

· possible causes of interrupts 可能的中断原因

· applications of interrupts 中断的应用

· use of an Interrupt service (ISR) handling routine 使用中断服务 (ISR) 处理例程

· when interrupts are detected during the fetch-execute cycle 在获取执行周期中检测到中断时

· how interrupts are handled 如何处理中断

- Interrupt中断的原因包括:

- a fatal error in a program 程序中的致命错误

- a hardware fault 硬件故障

- a need for I/O processing to begin 需要进行输入/输出

- user interaction 用户交互

- a timer signal 定时器信号

- 在执行完取码、解码和执行阶段后,会检查是否发生了中断。如果没发生,则正常运行。如果出现了中断,则进行相应的处理。

- 可通过设置interrupt register中断寄存器来识别不同的中断,其在每个单独的bit位中都存放着特定类型的中断。

- 中断会按照以下步骤进行处理和恢复:

- 在安全位置储存好程序计数器(PC)和各类寄存器的数值。

- 使用Interrupt Service Routine(ISR)将中断调入程序计数器,开始进行中断的处理。如果有多个中断,则按照优先级从高到低的顺序进行调入。

- 每执行完毕一个中断,都会检查是否有其他中断需要处理,有则重复上述过程,没有则将在安全位置储存好的程序计数器(PC和各类寄存器的数值调入CPU,继续中断之前的程序。

4.2 Assembly Language 汇编语言

- 大纲要求

4.2.1 Show understanding of the relationship between assembly language and machine code 理解汇编语言和机器码之间的关系

- machine code:机器码,指由一系列指令组成的代码,是CPU唯一能够识别的语言代码,能够直接控制指令的执行。

- 每个指令包含一个opcode操作码。

- 指令中可能不存在operand操作数,也可能存在最多三个operand操作数。

- 不同处理器的机器码不一样。

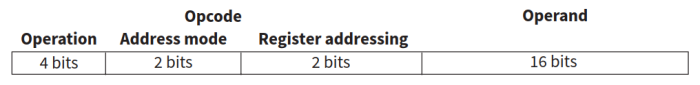

- 需要为每个机器码指定总位数、操作码的位数及位置、操作数的数量。比如下图中的机器码可分为:8位的opcode操作码和16位的operand操作数。

- assembly language:汇编语言,用于电子计算机、微处理器、微控制器或其他可编程器件的低级语言,亦称为符号语言。

- 每条机器码都有等效的汇编语言对应。运行时,汇编语言先要通过翻译程序翻译成对应的机器码,然后计算机才能识别并操作。

- 汇编语言包括opcode操作码的助记符和operand操作数的字符表示(地址)。

- 汇编语言允许程序员使用comments评论、symbolic names for constants常量的符号名称、labels for addresses地址标签、macros宏、directives指令等内容,使得程序编写更加容易、直观。

4.2.2 Describe the different stages of the assembly process for a two-pass assembler 描述两遍组装器组装过程的不同阶段

Apply the two-pass assembler process to a given simple assembly language program 将两遍汇编程序应用于给定的简单汇编语言程序

- two-pass assembler :二次扫描汇编程序。由于一些程序中出现的新符号在之前没有定义过,所以进行一次扫描时可能会出错,因此需要多数汇编程序会采用二次扫描,即第一次扫描列出符号表,第二次扫描列出对照表。

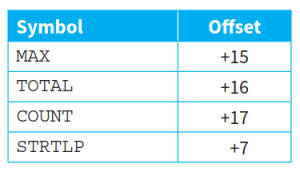

- 第一次扫描时,得到符号表。记录下每个出现过的符号,并同时记录下该符号被定义时的地址相对于base address基址的偏移量,如下图所示。该偏移量的二进制表示可作为operand操作数使用。

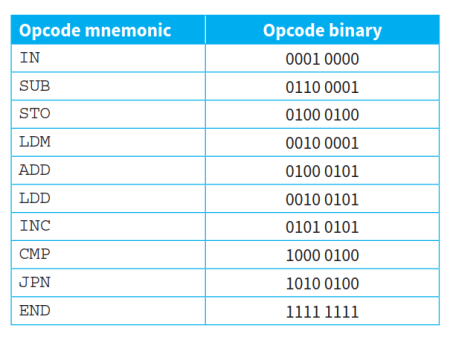

- 第二次扫描时,得到对照表。对每个符号,给出一个对应的opcode binary操作码二进制数字。如下图所示:

- 将二进制表示的操作码与操作数连接起来,构成机器码。如下图所示:

- 注意:该代码不会直接被执行,加载到内存中时还会更改地址,但作为汇编程序的输出仍是有效的。

4.2.3 Trace a given simple assembly language program 跟踪给定的简单汇编语言程序

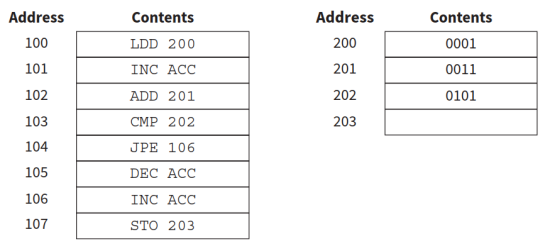

- Trace:追踪,即按照程序,观测每个地址内的值的变化情况。需要画出trace table。如下图所示:

4.2.4 Show understanding that a set of instructions are grouped 表明理解一组指令是分组的

Including the following groups: 包括以下群体:

· Data movement 数据移动

· Input and output of data 数据的输入和输出

· Arithmetic operations 算术运算

· Unconditional and conditional instructions 无条件和有条件指令

· Compare instructions 比较指令

- Data movement 数据移动:该类型的指令能够将数据加载到寄存器或存储到内存中。常见的类型如下图所示:

- Input and output of data 数据的输入和输出:使用IN和OUT对数据进行输入和输出。这两条指令仅有opcode操作码,没有operand操作数。

- IN:输入指令,用于在ACC中储存键盘输入字符的ASCII码的数值。

- OUT:输出指令,用于在屏幕上展示储存于ACC中的值对应的ASCII码字符。

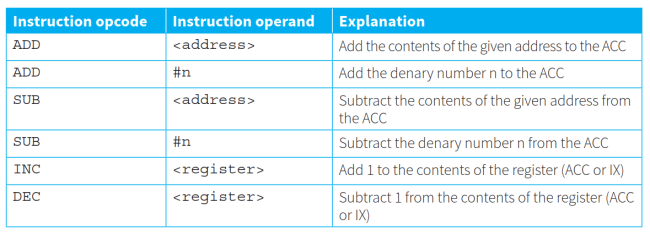

- Arithmetic operations 算术运算:职阶的算术运算仅支持加减,如果进行乘除运算,需要转化成连加或连减来进行。常见的类型如下图所示:

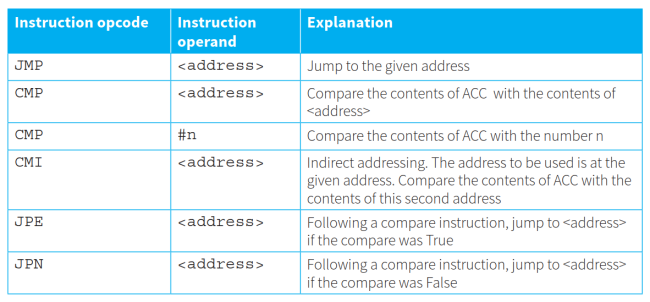

- Unconditional and conditional instructions 无条件和有条件指令:

- Unconditional instruction:无条件指令,无需进行比较就直接跳转到指定地址,继续进行程序。

- Conditional instruction:有条件指令,跳转前需要先进行比较,满足条件才会进行跳转。

- Compare instructions 比较指令:通过比较ACC存储的数据与指定地址内的数据,做出相应操作。常见的类型如下图所示:

- 注意:比较指令仅能判断二者是否相等。

- 比较的结果会被记录在status register状态寄存器的flag标志中,程序在判断是否执行跳转时,会查看flag是否被标记。

- 跳转指令运行时,program counter程序计数器会从新地址重新加载下一条指令,覆盖掉原有内容,然后才完成jump跳转,从新位置开始向下执行程序。

4.2.5 Modes of addressing 寻址方式

Including Immediate, direct, indirect, indexed, relative 包括即时、直接、间接、索引、相对

- Addressing mode:寻址方式。指各类通过operand操作数寻找到相应数值的方法。这些数值找到后会被导入register寄存器内进行下一步操作。常见的寻址方式如下:

- Absolute addressing:绝对寻址。编译指令的操作数是完整的地址编号。

- Relative addressing:相对寻址。编译指令的操作数以“base address基址+offset相对偏移量”表示。(基址的值不会改变)

- Indexed addressing:变址寻址。编译指令的操作数是由index register(IX)变址寄存器中的值与偏移量合成的地址(用IX中存的数值加上偏移量,得出新地址。IX内的值可能会不断改变)。

- Immediate addressing:即时寻址。编译指令的操作数是用在指令中的值。

- Direct addressing:直接寻址。编译指令的操作数是包含着用在指令中的值的地址。

- Indirect addressing:间接寻址。编译指令的操作数是地址,该地址包含着用在指令中的值的地址。

4.3 Bit manipulation 位操作

- 大纲要求

4.3.1 Show understanding of and perform binary shifts 展示对二进制移位的理解和执行

logical, arithmetic and cyclic 逻辑、算术和循环

Left shift, right shift 左移、右移

- logical, arithmetic and cyclic 逻辑、算术和循环

- Logical left shift:逻辑左移位。将二进制码的每一位向左移动一位,最高位进入carry bit进位位(但不再显示),最低位以0填充。比如00110001左移,得到01100010。

- 当二进制的最高位为0且无符号时,左移后的数字相当于原数字的2倍。(以十进制来看)

- Logical right shift:逻辑右移位。将二进制码的每一位向右移动一位,最低位进入carry bit进位位(但不再显示),最高位以0填充。比如00110001右移,得到00011000。

- 当二进制的最高位为0且无符号时,右移后的数字相当于原数字的1/2。(以十进制来看,取整)

- Logical left shift:逻辑左移位。将二进制码的每一位向左移动一位,最高位进入carry bit进位位(但不再显示),最低位以0填充。比如00110001左移,得到01100010。

- Arithmetic shift:算术移动。其过程和上述逻辑移动类似,但符号位不参与移动,永远在二进制码的首位。其他位的移动规则和logical shift一致。

- Cyclic shift:循环移动。其过程和上述逻辑移动类似,但移动入进位位的数字将会在另一端再次出现。(构成环状)

4.3.2 Show understanding of how bit manipulation can be used to monitor / control a device 了解如何使用位操作来监控/控制设备

Carry out bit manipulation operations 进行位操作操作

Test and set a bit (using bit masking) 测试并设置位(使用位掩码)

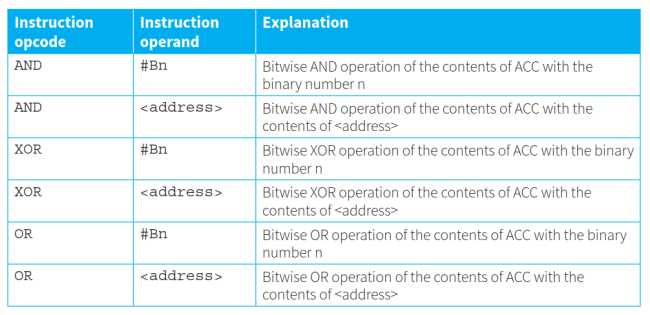

- Carry out bit manipulation operations 进行位操作操作

- 使用bitwise logic operation instruction位逻辑操作指令进行运算,可以掩盖某些位而达到只影响某些位的目的。这些指令的operand操作数被称为mask掩码。常见的位操作如下图所示:

- Test and set a bit (using bit masking) 测试并设置位(使用位掩码)

- AND位操作:选定位保持不变,其他位清零。

- OR位操作:选定位赋1,其他位保持不变。

- XOR位操作:让选定位的数值反转(从0变成1,或从1变成0)。